Only one of the FPUs supports 32-bit interger instructions.

Since the throughput of FP64 instructions are 2 cycles, the FP32 FLOPS is a quarter of the FP64 FLOPS. One supports FP32 and FP64, and the other supports only FP32. Each EU contains 2 × 128-bit FPUs and has double peak performance per clock cycle compared to previous generation.Specifications of Intel HD Graphics series Graphics The entire GPU shares a sampler and an ROP.Double peak performance per clock cycle compared to previous generation due to fused multiply-add instruction.Each EU has a 128-bit wide FPU that natively executes eight 16-bit or four 32-bit operations per clock cycle.Each EU has a 128-bit wide FPU that natively executes four 32-bit operations per clock cycle.

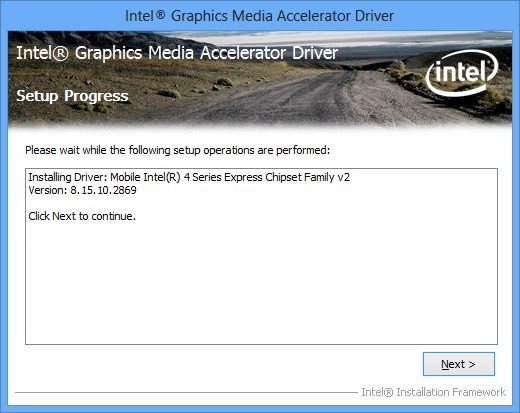

The fourth generation consists of Shader Model 3.0 and 4.0 integrated graphics with hardware support for both vertex and pixel shaders. Intel released its latest generation of integrated GMA chipsets. Variable-Length Decoding (VLD) + iDCT + MC (Full) Even though they are DirectX 9 compliant, vertex shaders are created in software by the CPU, resulting in some games not working due to the missing on hardware vertex shaders. Third generation consists of integrated graphics processing units with DirectX 9 support.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed